-

短波红外辐射是指波长为0.9 ~3 μm的红外辐射,广泛存在于自然界中,其主要来源有自然环境的反射和高温物体的辐射等。常见的用于制造短波红外焦平面探测器的材料主要包括:InGaAs,HgCdTe和InAs等。其中InGaAs器件因其优异的综合性能,比HgCdTe器件更高的电子迁移率,更低的衬底与外延材料间的晶格失配,高灵敏度,能够在室温和近室温工作,工艺成熟等优点被广泛应用于军事、工业、医学等领域[1]。

随着材料工艺水平和CMOS工艺水平的不断提高,InGaAs探测器向着高分辨率、高灵敏、多波段、数字化等方向发展,其中数字化InGaAs探测器技术是一个重要的发展方向。数字化InGaAs探测器技术不同于传统的在模拟域读出光电信号再在片外的成像电路上进行数字化的工作模式,其通过将光电流信号在片内数字化,实现信号的数字化传输,一方面可以突破模拟信号传输带宽对于探测器分辨率和帧频的限制,另一方面可以降低信号传输过程中的串扰、噪声等对于探测器性能的影响,从而提高探测器的各方面性能。

文中首先简单介绍了国内外InGaAs探测器技术发展现状,然后介绍了用于640×512面阵规格,15 μm像元中心距的数字化读出电路,最后给出了数字化InGaAs探测器组件的测试结果和成像图片。

-

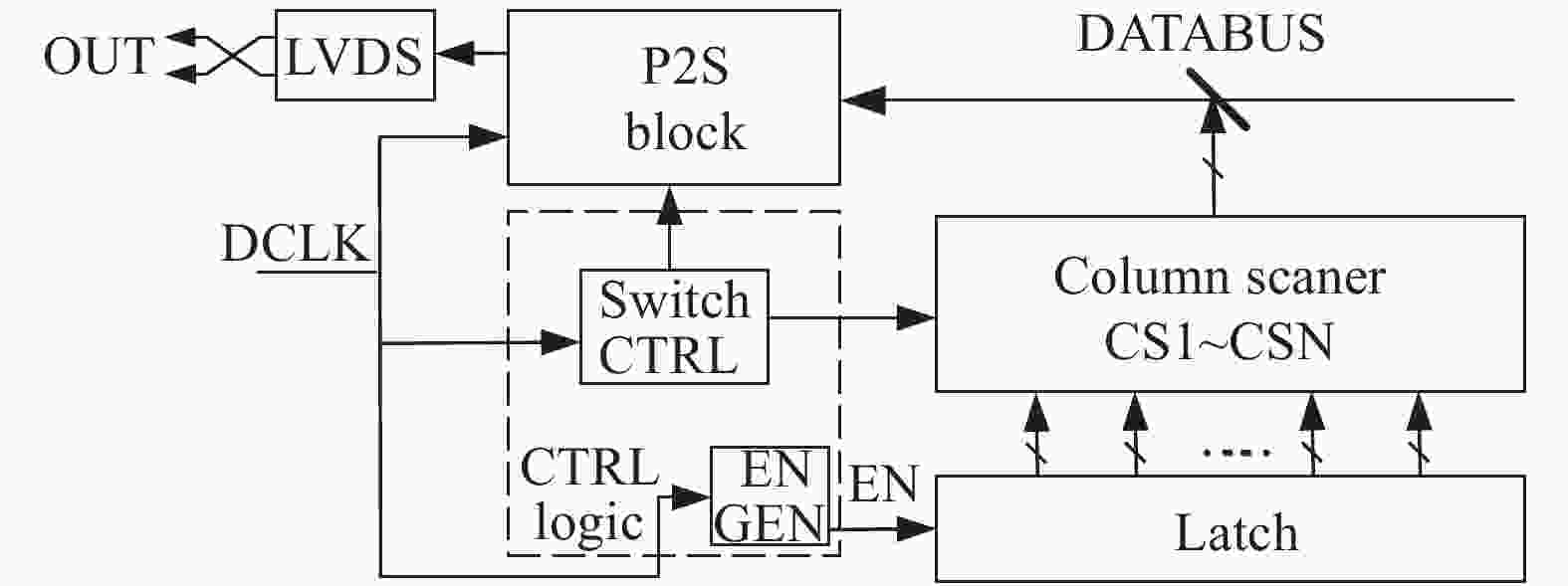

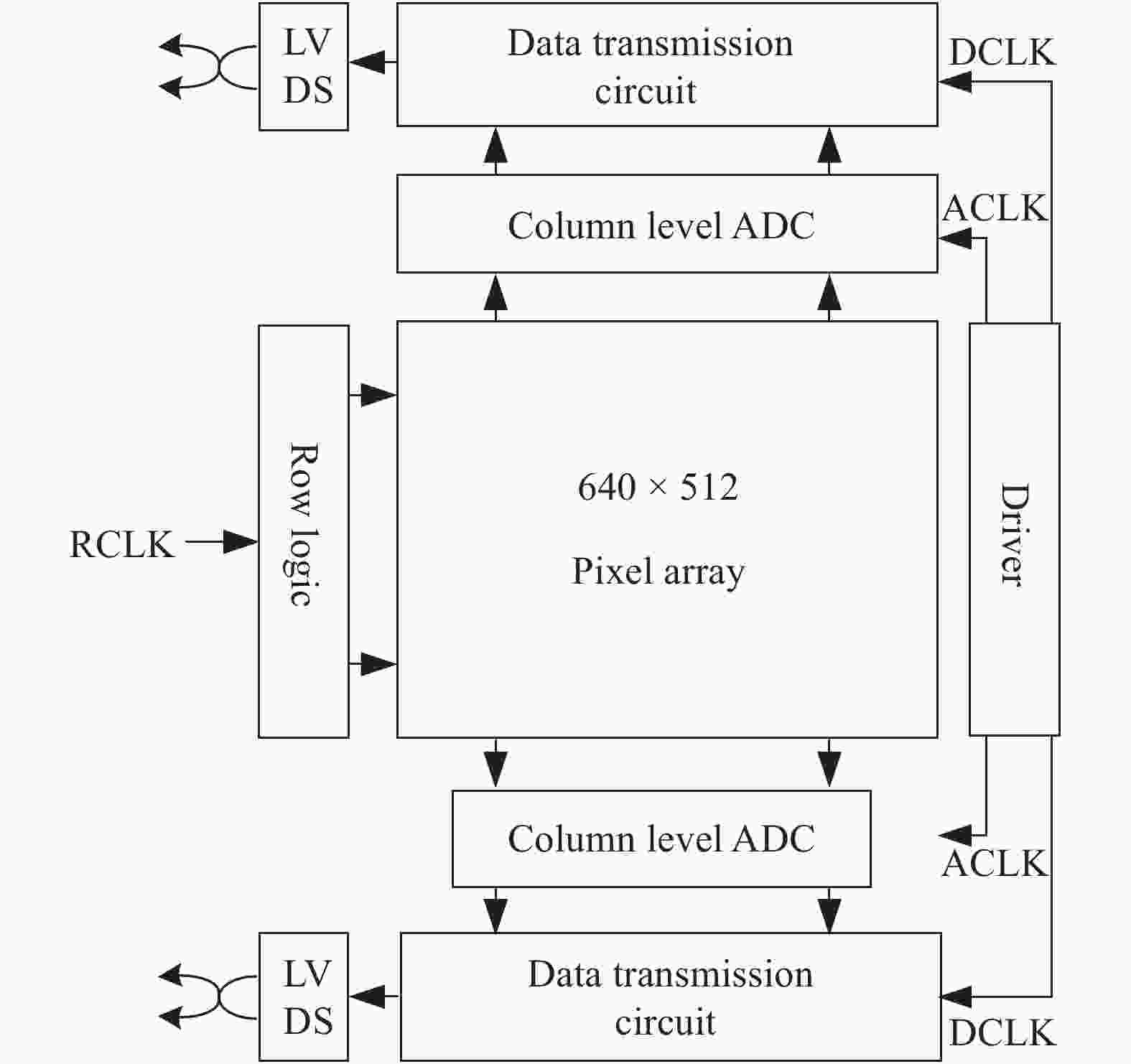

数字化读出电路技术是数字化InGaAs探测器技术的核心,其通过将模拟-数字转换器(ADC)集成到读出电路中实现数字化读出电路。根据ADC集成方式的不同,数字化读出电路也有以下三种结构:片级数字化读出电路,列级数字化读出电路和像素级数字化读出电路。其中片级数字化读出电路在读出电路中只集成一个或若干个ADC,本质上与传统模拟读出电路并无差别;列级ADC数字化读出电路在每列都采用一个ADC对信号进行数字化,读出电路的行多路器工作在模拟域,列多路器工作在数字域,能够较好地改善探测器组件的性能;像素级ADC在每个像元内都集成一个ADC,探测器的光电信号在像元内就被数字化,所以读出电路的行多路器和列多路器都工作在数字域,对于整个探测器组件的性能提升最大。数字化读出电路对于ADC的基本要求是高分辨率、低功耗和小面积,其中高分辨率的性能要求是因为探测器光电信号动态范围较大的特点,要求ADC的分辨率达到14 bit以上,低功耗和小面积的要求与数字化读出电路的结构有关,具体来说:对于片级ADC数字化读出电路来说,ADC的功耗和面积没有太大限制;对于列级ADC数字化读出电路来说,由于每列都要集成一个ADC,整个读出电路包含上百个ADC,ADC的功耗必须严格控制,同时ADC的版图尺寸在一维方向上必须小于等于像元尺寸;对于像素级ADC数字化读出电路来说,由于在每个像元内都集成ADC,整个读出电路包含数十万个ADC,这对于ADC的功耗提出了极高的要求,同时ADC的版图尺寸在二维方向上都受到像元尺寸的严格限制,要在如此苛刻的版图面积内实现高分辨率低功耗的ADC具有非常大的难度,特别对于小光敏元探测器来说。因此,列级ADC数字化读出电路是一个较好的折中方案,也是目前主流的数字化读出电路结构。因此文中采用了列级ADC数字化读出电路架构,其结构框图如图1所示。

国外对于InGaAs探测器技术的研究起步较早,发展较快,目前已经有数字化InGaAs探测器组件的产品。例如,以色列的SCD公司于2014年推出了数字化InGaAs组件产品Cardinal 640,面阵规模是640×512,像元中心距为15 μm,它的读出电路与其代表性产品Pelican-D的读出电路相同,采用了13~15 bit可编程ADC[2],之后SCD公司又推出了Cardinal 1280 HD等产品,形成了系列产品。除此之外,美国的Sensor Unlimited公司,比利时的Xenics公司,以及法国的Sofradir公司等虽然未见数字化InGaAs探测器产品,但致力于降低暗信号散粒噪声,提升产品的信噪比和灵敏度,陆续发布了基于各种应用的性能优越的InGaAs探测器产品,例如,Sensor Unlimited公司的640 CSX产品[3],Xenics公司的T2SL产品[4],以及法国的Snake SW产品等[5]。

国内的InGaAs探测器技术虽然起步较晚,但也取得了一定的成果。例如,重庆光电技术研究所研制的GD6882-NIR320-MD型混成式InGaAs焦平面探测器,其分辨率为320×256,并基于该探测器实现了成像组件的设计,在微光条件下获得了清晰的成像图片[6];此外,重庆光电技术研究所也对雪崩焦平面进行了研究,其设计的32×32面阵规格的盖革模式雪崩焦平面阵列,实现了激光三维成像探测功能[7]。中国科学院上海技术物理研究所对线列型数字化InGaAs探测器进行了研究,其面阵规格是256×1,采用逐次逼近型ADC,但未见成像[8]。除了数字化组件外,上海技术物理研究所也设计并实现的800×2,320×256,以及640×512等规格的模拟InGaAs探测器组件,获得了清晰的成像图片[9]。

-

列级ADC数字化读出电路主要包括三个组成模块:读出单元电路,列级ADC和数据传输电路。下文对各模块的设计进行了介绍。

-

读出单元电路负责对探测器的光电流进行积分,将电流信号转换成电压信号,然后通过内部的缓冲器(buffer)将其读出,它是整个读出电路和探测器的接口,其非线性度显著影响着整个探测器组件的性能,也为后续的图像处理带来不便。传统读出单元电路的电路图如图2(a)所示,输出buffer通常采用源极更随器来实现。源极跟随器的优点是电路结构简单,在每个读出单元电路中只有一个晶体管,节省了版图面积。源极跟随器的缺点是较大的非线性,原因在于源极跟随器输入管M1的衬底偏置效应和沟道长度调制效应。源极跟随器输入电压Vin和输出电压Vout的关系可以通过以下公式表征:

$${i_d} = \frac{\beta }{2}{\left( {{V_{{{{\rm{out}}}}}} - {V_{{{{\rm{in}}}}}} + {V_{{\rm{th}}}}} \right)^2}(1 + \lambda {V_{{{{\rm{out}}}}}})$$ (1) $${V_{{\rm{th}}}} = {V_{{\rm{th}}0}} + \gamma \left( {\sqrt {|2\varPhi + {V_{{\rm{out}}}}|} - \sqrt {2\varPhi } } \right)$$ (2) $$\beta = \propto \frac{W}{L}$$ (3) 式中:W和L分别是M1的宽度和长度;λ是沟道长度调制系数;γ是体效应系数;Vth0

是晶体管的本征阈值电压;Φ是工艺相关的系数。可以看到衬底偏置效应和沟道长度调制效应都会对输出引入非线性。对于PMOS晶体管,可以通过将其衬底接到源极来消除衬底偏置效应,但是在版图实现上设计规则要求不同的衬底必须互相远离,因此这将消耗版图面积,对于小面积的读出单元电路实现十分不利。

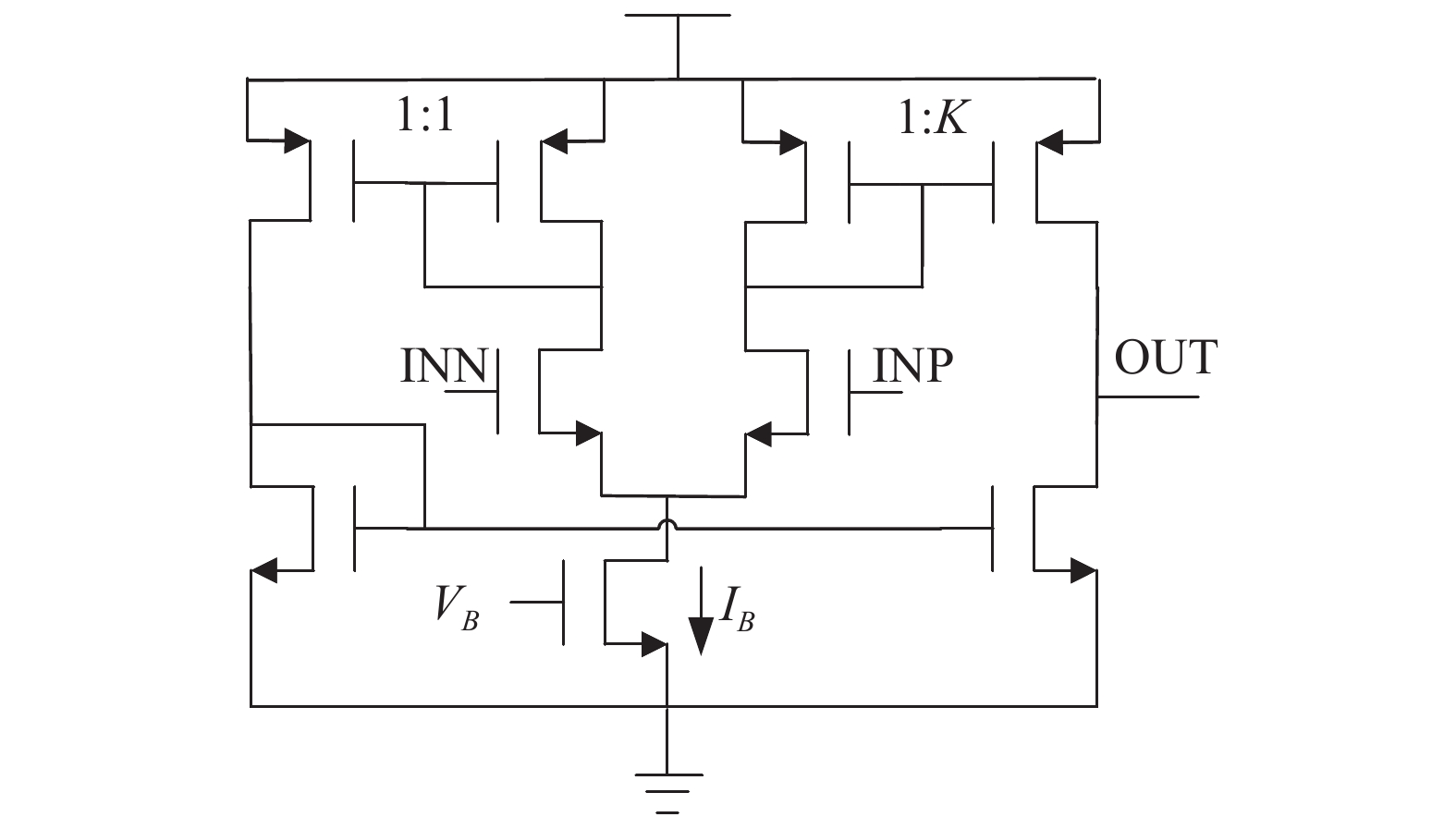

图 2 (a) 传统读出单元电路,(b) 所设计的输出buffer和读出单元电路

Figure 2. (a) Conventional readout unit circuit diagram, (b) readout unit circuit with the proposed buffer

文中所设计的输出buffer如图2(b)所示,显然,所设计的buffer的架构脱胎于差分放大器的输入级。可以看到,如果差分放大器的晶体管M1和M2相同,且流过它们的电流相等,那么Vinp和Vinn也必然相等,因此只需要在传统的源极跟随器结构的基础上增加一个相同的晶体管,并且设计i4=i3/2即可保证Vin和Vout完全相等。消除了衬底偏置效应引入的非线性以及单源极跟随器的输出电压偏置。所设计的读出单元电路的整体电路图如图2(b)所示,增加的晶体管置于读出单元电路之外,因此读出单元电路内的电路结构与传统结构完全相同。

所设计的读出单元电路采用全局曝光(snap shot / global shutter)结构,所有像元同时开始积分,积分结束后将积分电容上的电荷转移到采样保持电容上,然后逐行读出,当读出单元电路完成电荷转移后就可以开始下一帧信号的积分,实现边积分边读出(IWR)的工作模式。

-

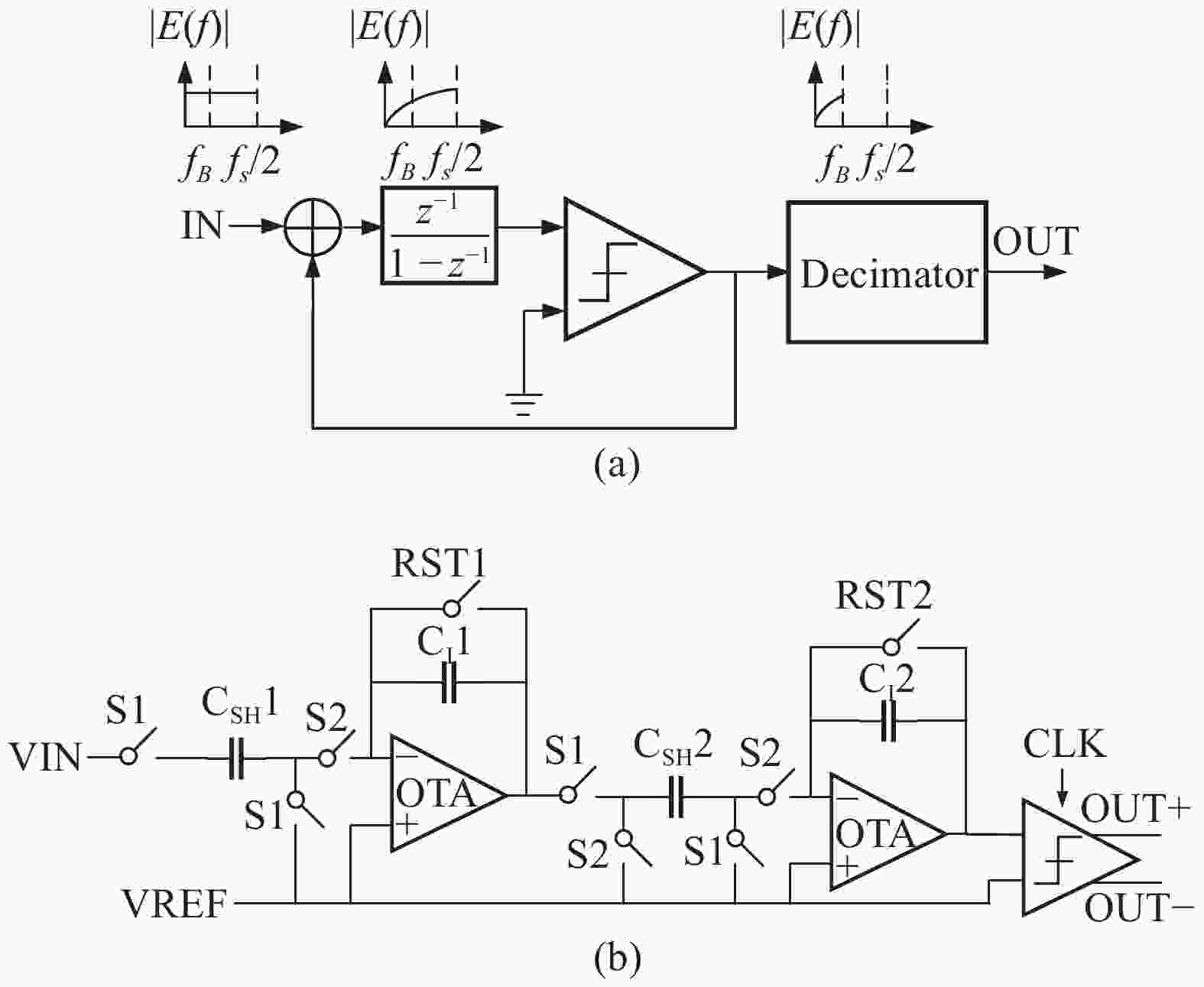

列级ADC数字化读出电路对于ADC的要求是:高分辨率,低功耗,中等转换速率,以及小面积。在众多ADC结构中逐次逼近型(SAR) ADC和Sigma-Delta ADC是较为合适的结构,其中SAR ADC具有较快的转换速率和较低的功耗[10-11],而Sigma-Delta ADC在精度上更具有优势。考虑到列级ADC高分辨率的要求,Sigma-Delta ADC是更好的选择,其基本原理是通过过采样技术将量化噪声分布在整个采样频带,然后通过调制器(Modulator)将基带噪声调制到高频,最后通过数字抽取滤波器(Decimator)将高频的噪声滤除,并输出最终的转换结果,如图3(a)所示。

由于读出单元电路的输出是直流电压信号,因此可以将传统Sigma-Delta ADC的调制器和数字抽取滤波器每个采样周期进行复位,这就得到了Incremental Sigma-Delta ADC[12]。Incremental Sigma-Delta ADC作为Sigma-Delta ADC的一种改进结构,不仅继承了传统Sigma-Delta ADC的过采样技术和噪声整形技术,而且通过将调制器和数字抽取滤波器每个采样周期进行复位,使得数字抽取滤波器可以通过简单的累加器结构来实现,改善了传统数字抽取滤波器结构复杂以及功耗较大的缺点。尽管如此,Incremental Sigma-Delta ADC应用于列级ADC数字化读出电路还是难以胜任。一方面来说,单级的调制器对于噪声的调制作用有限,对于ADC的性能有所限制。另一方面,Incremental Sigma-Delta ADC共需214个时钟周期来完成一次14 bit的转换,对于640×512阵列的InGaAs探测器组件,在帧频为60 Hz的情况下,ADC的时钟频率fACLK

大于503 MHz,数百个ADC同时高速工作将消耗数百毫瓦的功耗,而且对电路设计提出较大挑战。

图 3 (a) 传统Sigma-Delta ADC结构框图,(b) 二阶Incremental Sigma-Delta 调制器结构框图

Figure 3. (a) Traditional Sigma-Delta ADC diagram, (b) second order Incremental Sigma-Delta modulator diagram

为了解决Incremental Sigma-Delta ADC的上述缺陷,将调制器级联起来形成高阶Incremental Sigma-Delta ADC是较好的思路。对于L阶的调制器来说,其系统传输函数

$Y\left( z \right)$ 可以表示为:$$ Y\left( z \right) = {z^{ - L}}X\left( z \right) + {\left( {1 - {z^{ - 1}}} \right)^{ - L}}E\left( z \right) $$ (4) 定义噪声传递函数

$ E\left( z \right)$ 的表达式为:$$ E\left( z \right) = {\left( {1 - {z^{ - 1}}} \right)^{ - L}} $$ (5) 则其幅频响应

$ E\left( f \right)$ 可以表示为:$$ \left| {E\left( f \right)} \right| = {2^{2L}}{\rm{si{n}}^{2L}}\left( {\pi f/{f_s}} \right) $$ (6) 从公式(6)中可以看到随着阶数L的增大,调制器将基带噪声推往高频的效果越明显,即ADC的噪声整形能力越强。但是三阶及以上的Incremental Sigma-Delta ADC具有系统稳定性问题,所以二阶结构是较为常用的结构。

与此同时,二阶Incremental Sigma-Delta ADC,只需要

${2^{\left( {14 + 1} \right)/2}}$ 个时钟周期就能完成14 bit的转换,对于640×512阵列的InGaAs探测器组件,在帧频为60 Hz的情况下,${\rm{}}{f_{{\rm{ACLK}}}}$ 只需大于5.5 MHz,相比相同精度要求的传统一阶Incremental Sigma-Delta ADC的503 MHz,降低了99%。二阶Incremental Sigma-Delta 调制器的电路结构如图3(b)所示。

调制器的核心部分是放大器(OTA),考虑到放大器的驱动能力,其输出晶体管用AB类偏置[13]。如图4所示,不同于两端电流拷贝比例均为1:K的传统AB类结构,所设计的放大器两边的电流镜采取了非对称设计:一端的电流拷贝比例为1:K,而另一端的电流拷贝比例为1∶1[13]。其消耗的总电流I如公式(7)所示。

$$ I = {I_B} + \frac{{1 + K}}{2}{I_B} $$ (7) 相比传统结构消耗的总电流

$ I'$ $$ I' = {I_B} + K{I_B} $$ (8) 电流消耗减小了(K-1)IB/2,其中IB是放大器的偏置电流。

数字化读出电路列级ADC的放大器的增益带宽积设计为25 MHz,为ADC时钟频率的五倍左右。由于Incremental Sigma Delta ADC对于电路失调和失配等信息不敏感,为了进一步减小调制器的功耗,比较器采用了动态结构。

调制器的输出送入数字抽取滤波器进行进一步处理。数字抽取滤波器有两个主要功能:滤除高频的噪声和将得到的信号,进行下采样,为将来的数字信号处理做准备。图5(a)展示了用于传统二阶Sigma Delta ADC的数字抽取滤波器,它是sinc滤波器,一共由56个加法器和延时单元组成,数据运算量较大,特别是工作于高时钟频率fACLK的两个积分器,该电路不但结构复杂而且消耗较大的功率。

图 5 (a) 2阶Sigma-Delta 数字抽取滤波器结构框图,(b) 2阶Incremental Sigma-Delta 数字抽取滤波器结构框图

Figure 5. (a) Second order Sigma-Delta decimator, (b) second order Incremental Sigma-Delta decimator

Incremental Sigma Delta ADC的数字抽取滤波器每个采样周期进行复位,不再持续工作,所以可以通过简单的累加器结构来实现,无需采用由多级积分器和微分器组成的sinc滤波器,其电路结构和功耗都得到了很大程度的改善。如图5(b)所示,8 bit纹波计数器(ripple counter)以及15 bit加法器和锁存器分别构成2级积分器。

-

数据传输电路的功能是将所有ADC的并行数据转换为串行,并在一帧时间之内完成所有数据的读出。对于量化位数为14 bit的640×512面阵的InGaAs探测器组件,在帧频为60 Hz的条件下,读出电路的数据率达到了275 Mbps,所以必须采用高速数据传输电路。

传统的数据传输电路由N个D触发器(DFF)组成移位寄存器将数据串行移出(N为探测器的列数),数据之间的传递线路较短,整个数据传输电路可以工作于较快的速率,在CMOS 0.35 μm工艺下,这个速率可以达到500 MHz以上,而且随着CMOS工艺的提升,该速率可以进一步加快。但是,该结构有一个问题,由于所有的DFF同时工作在高速的主时钟频率fDCLK,其消耗的功率较高。传统的数据传输电路的功耗Pt的表达式如公式(9)所示。其中

$ B$ 为ADC的量化位数,PDFF为单位频率下DFF平均消耗的功率。$$ {P_t} \approx N \times B \times {f_{DCLK}} \times {P_{DFF}} $$ (10) 在CMOS 0.35 μm的工艺下PDFF约为0.4×10−12 W,对于量化位数为14 bit的640×512面阵的InGaAs探测器组件,在帧频为60 Hz的条件下,fDCLK为275 MHz,所以传统的数据传输电路的功耗可以达到数百毫瓦。如何减小持续工作在高速时钟下的电路模块是减小数据传输电路功耗的关键。

为此,设计了新型的数据传输电路,其整体架构和时序图如图6所示。整个数据传输电路主要由锁存器,列选单元和并串转换器组成。锁存器将ADC的数据进行存储,然后在逻辑单元的控制下逐列通过数据总线传输到并串转换器转换成串行数据。由于整个电路中只有并串转换器持续工作在最高时钟频率,而并串转换器同一时刻只对一个ADC的数据进行转换,所以并串转换器只需要14个DFF。也就是说整个数据传输电路只有14个DFF同时工作在最高时钟频率,其功耗PPP如公式(10)所示。可以看到其功耗仅为传统结构的1/512。

$$ {P_{PP}} \approx 14 \times {f_{DCLK}} \times {P_{DFF}} $$ (11) -

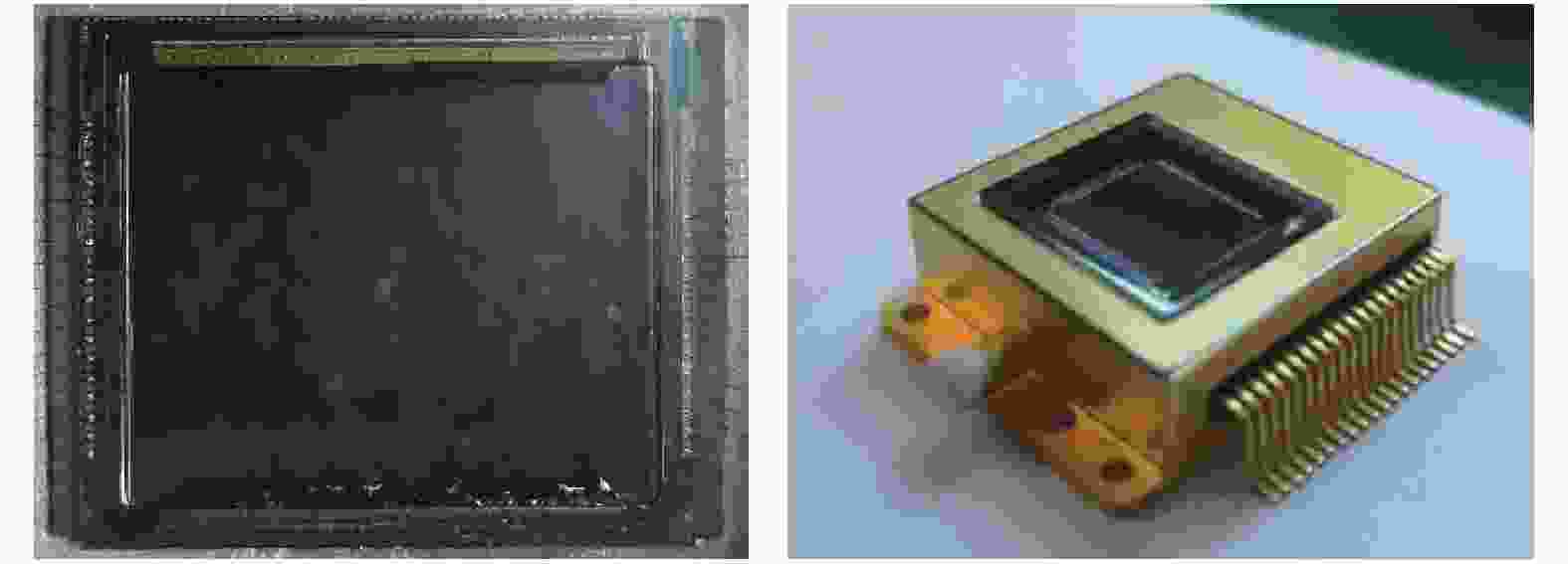

640×512列级ADC数字化读出电路采用0.35 μm标准CMOS工艺实现。

在利用0.35 μm标准工艺实现数字化读出电路晶圆之后,将读出电路芯片与InGaAs探测器阵列芯片通过铟柱倒装互联实现InGaAs数字化焦平面探测器组件。探测器芯片照片和封装如图7所示。基于自主开发的测试平台,对所设计的探测器组件进行了测试,测试方法是通过测试电路板为探测器组件提供所需的偏置电压和驱动信号,然后通过CameraLink接口将数据采集到PC端并进行计算,最终得到测试结果。

图 7 InGaAs探测器芯片和封装照片

Figure 7. Pictures of InGaAs detector chip and digital InGaAs detector assembly

在无光照的条件下,经过大量的图像数据采集测得读出电路在常温下的RMS噪声为1.5 LSB,约等于230 μV,小于传统模拟读出电路的噪声,如图8(a)所示。

图 8 读出电路测试结果。(a)噪声测试结果,(b)线性度测试结果

Figure 8. Test result of ROIC. (a) Noise test result, (b) linearity test result

通过固定光电流输入,改变积分时间的方法对读出电路的线性度进行了测算。读出电路对相同的光电流进行不同时间的积分以获得不同的电压信号,然后将该电压通过列级ADC量化,最后输出至片外,所以其输出值的线性度表征了读出电路的注入级电路、读出单元电路的输出buffer、以及ADC的线性度,也即整个读出电路的线性度。图8(b)展示了在均匀黑体前,不同积分时间下的探测器输出曲线,拟合曲线的标准差为0.15%,表明了读出电路具有较好的线性度。

得益于列级ADC和数据传输电路的低功耗设计,在60 Hz帧频下整个读出电路的功耗仅为94 mW,与传统的模拟读出电路功耗相当。

表1归纳了所介绍的数字化InGaAs探测器组件的性能指标与国外产品的对比。从指标上看文中介绍的数字化InGaAs探测器组件在面阵规格、量子效率和ADC位数等方面与国外各大厂商的产品基本处于同一技术水平,但探测率相比国外厂商仍有差距。

所设计的数字化InGaAs探测器组件搭配不同的光学镜头制作成了成像样机,如图9(a)所示。采用不同的光学镜头就可以实现不同环境的应用需求。图9(b)和图9(c)展示了白天室外近景和远景的成像效果,由于数字化探测器较好的信噪比和抗干扰性,成像清晰无杂波干扰。

表 1 各款InGaAs探测器组件性能参数表和性能对比

Table 1. Comparison of performance among different InGaAs detector products

Parameter This work SCD Cardinal 640 Sensor Unlimited CSX 640 Sofradir Snake SW Format 640×512 640×512 640×512 640×512 Pitch/μm 15 15 12.5 15 Spectral range/μm 0.9-1.7 0.9-1.7 0.7~1.7 0.9-1.7 Quantum efficiency 65%@1.6 μm 80%@1.55 μm 65 %0.9 µm-1.6 µm 70 %1 µm-1.6 µm Detectivity, D* /cmHz1/2W-1 1×1012@300 K -- 2.8×1013@293 K -- Reading mode IWR IWR IWR IWR ADC 14 14 -- -- Max frame rate/Hz 120 350 -- 300

图 9 (a) 640×512数字化InGaAs热像仪样机,(b) 640×512数字化InGaAs热像仪样机近景成像图片,(c) 640×512数字化InGaAs热像仪样机远景成像图片

Figure 9. (a) Prototype of 640×512 digital InGaAs thermal IR imager, (b) close shot captured by the prototype of 640×512 digital InGaAs thermal IR imager, (c) distant view captured by the prototype of 640×512 digital InGaAs thermal IR imager

-

文中介绍了昆明物理研究所的640×512数字化InGaAs探测器组件的设计和测试。所设计的数字化InGaAs探测器组件采用列级ADC数字化读出电路,通过高线性度读出单元电路设计,高精度、低功耗列级ADC设计,和低功耗数据传输电路设计,最终实现了高性能的数字化读出电路设计。所设计的数字化读出电路基于350 nm标准CMOS工艺进行了流片,并与InGaAs探测器进行了倒装互联和封装,实现了数字化InGaAs探测器组件。测试结果表明,探测器组件的读出噪声为230 μV,峰值量子效率为65%,在300 K下的探测率为1×1012 cm·Hz1/2/W,在60 Hz帧频下,功耗为94 mW,与传统的模拟InGaAs探测器组件相当。通过对数字化InGaAs探测器组件的设计和测试表明,数字化InGaAs探测器组件具有低读出噪声,高线性度,高传输带宽,高抗干扰性等特点。

640×512 digital InGaAs detector assembly

-

摘要: 数字化InGaAs探测器是短波红外探测器技术发展的一个重要方向,它不仅可以提升系统的集成度,还可以提升成像系统的各项技术指标。通过将模拟-数字转换器(ADC)集成到读出电路中实现数字化读出电路是数字化InGaAs探测器的技术核心。文中介绍了640×512数字化读出电路的设计与实现,并与InGaAs探测器通过铟柱进行倒装互联形成了数字化InGaAs探测器组件。通过对探测器组件的测试得到读出噪声为230 μV,峰值量子效率为65%,在300 K温度下探测率为1.2×1012 cmHz1/2/W,在60 Hz帧频下功耗为94 mW。测试结果表明,数字化InGaAs探测器组件具有低读出噪声,高线性度,高传输带宽,高抗干扰性等特点。Abstract: Digital InGaAs detector significantly orients the development of short wave (SW) infrared detector technology, it not only can increase integrated level of the system, but also can develop the imager’s performance. The key point to realize the digital InGaAs detector is integrating ADC into the readout integrated circuit (ROIC) and realize digital ROIC (DROIC). The 640×512 DROIC was designed and fabricated, it interconnected InGaAs detector focal plane array with In and realized digital InGaAs detector assembly. The proposed digital InGaAs detector assembly was tested, and the measurement results show that its readout noise is 230 μV, peak quantum efficiency is 65%, detectivity under 300 K temperature is 1.2×1012 cm Hz1/2 / W, and the power consumption is 94 mW when frame rate is 60 Hz. The measurement results indicate that the digital InGaAs detector assembly has some features as low readout noise, high linearity, wide transmission bandwidth, good resistance to interference and so on.

-

Key words:

- InGaAs detector /

- digital readout circuit /

- column level ADC /

- digital detector assembly

-

图 9 (a) 640×512数字化InGaAs热像仪样机,(b) 640×512数字化InGaAs热像仪样机近景成像图片,(c) 640×512数字化InGaAs热像仪样机远景成像图片

Figure 9. (a) Prototype of 640×512 digital InGaAs thermal IR imager, (b) close shot captured by the prototype of 640×512 digital InGaAs thermal IR imager, (c) distant view captured by the prototype of 640×512 digital InGaAs thermal IR imager

表 1 各款InGaAs探测器组件性能参数表和性能对比

Table 1. Comparison of performance among different InGaAs detector products

Parameter This work SCD Cardinal 640 Sensor Unlimited CSX 640 Sofradir Snake SW Format 640×512 640×512 640×512 640×512 Pitch/μm 15 15 12.5 15 Spectral range/μm 0.9-1.7 0.9-1.7 0.7~1.7 0.9-1.7 Quantum efficiency 65%@1.6 μm 80%@1.55 μm 65 %0.9 µm-1.6 µm 70 %1 µm-1.6 µm Detectivity, D* /cmHz1/2W-1 1×1012@300 K -- 2.8×1013@293 K -- Reading mode IWR IWR IWR IWR ADC 14 14 -- -- Max frame rate/Hz 120 350 -- 300 -

[1] Zhang Yonggang, Gu Yi, Shao Xiumei, et al. Short-wave infrared InGaAs photodetectors and focal plane arrays [J]. Chin Phys B, 2018, 12: 57−63. [2] Shkedy L, Koifman A. Multi-function InGaAs dector for swir imaging[C]//SPIE, 2014, 2930: 2930312. [3] Sensors Unlimited. Micro-SWIR 640CSX Camera [EB/OL]. [2016-12-01]. http://www.sensorsinc.com/products/detail/microswir-camera. [4] Xenics. Product Selector Guide [EB/OL]. [2017-05-03]. http://www.xenics.com/products/. [5] Sofradir. SWIR Detectors [EB/OL]. [2019-09-20]. https: //www. lynred. com/produit/snake-sw. [6] Yang Cunming, Lu Jie, Wen Zhongliu, et al. Study on imaging technology of InGaAs near-infrared camera [J]. Semiconductor Optoelectronics, 2014(3): 543−545. (in Chinese) [7] Zhang Xiuchuan, Gao Xinjiang, Chen Wei, et al. 32×32 InGaAs/InP Geiger-mode avalanche photodiode focal plane arrays[C]//The Second Symposium on Lidar Imaging Detection Technology and Application, 2015. (in Chinese) [8] Wei Y, Wang X Q. Digital output for short-wave infrared InGaAs linear FPA [J]. Journal of Infrared Millimwave, 2018, 37(3): 257−260. [9] Shao Xiumei, Gong Haimei, Li Xue, et al. Developments of highperformance short-wave infrared InGaAs focal plane detectors [J]. Infrared Technology, 2016, 38: 629−635. (in Chinese) doi: 10.11846/j.issn.1001_8891.201608001 [10] Chen D G, Tang F. A 64 fJ/step 9-bit SAR ADC array with forward error correction and mixed-signal CDS for CMOS image sensors[J]. IEEE Transactions on Circuits and Systems - I, 2014, 60(8): 2561-2566. [11] Rarbi R F, Dzahini D. An 8-bit, 100-MSPS fully dynamic SAR ADC for ultra-high speed image sensor [J]. International Journal of Electrical, Computer, Energetic, Electronic and Communication Engineering, 2018, 12(1): 1−6. [12] Robert J, Deval P. A second-order high-resolution incremental A/D converter with offset and charge injection compensation [J]. IEEE Journal of Solid-State Circuits, 1988, 23: 736−741. doi: 10.1109/4.313 [13] Yao Libin, Chen Nan. Compact, micro-power incremental Sigma-Delta ADC design [J]. Infrared Technology, 2013, 35(3): 125−132. (in Chinese) -

下载:

下载: