-

红外焦平面阵列(Infrared Focal Plane Array, IRFPA)成像技术,具有隐蔽性好、透烟雾、微光夜视等优点,在气象遥感、工业检测、医学影像、军事装备等领域获得了广泛应用。随着技术进步,IRFPA各项性能显著提高,但是表征空域噪声的非均匀性还比较差[1],严重制约着红外成像质量和应用性能。

读出电路(Read Out Integrated Circuit, ROIC)的非均匀性成为限制IRFPA发展的主要瓶颈[2]之一。由于IRFPA的非均匀性来源复杂且改进工艺难度大,多数研究集中在非均匀性校正算法方面[3-4]。读出电路方面,参考文献[5]利用三维噪声模型分析了读出电路噪声特性;参考文献[6-8]对不同结构读出电路的非均匀性进行了分析和仿真;参考文献[9]提出了一种带片上校正功能的读出电路;参考文献[10]利用读出电路结构特点对片外校正方法进行了改进。但是公开文献对于ROIC非均匀性的总体设计、分析和模拟方法缺乏清晰的理论分析和论述。

将非均匀性要素归纳为输入项和状态项,利用动态非线性系统方程的泰勒级数展开建立单元电路非均匀传输的一般模型解决单元电路结构的差异性问题;通过建立等维等长传输矩阵简化行列串并转换传输过程中的数模电路耦合过程,并根据模拟型读出电路的一般架构建立其非均匀性总体传输模型;通过引入柏林噪声[11]解决状态参数的空间局部相关性问题;采用三维噪声模型的空间分量表征非均匀性指标,对读出电路非均匀性进行数值模拟和统计分析,为读出电路的总体设计和工程优化提供有效的理论指导。

-

广义的非均匀性是指红外成像系统的单元输出量,即像素灰度数值的空间不一致性。狭义非均匀性一般指各种不同的非均匀性评价指标。由于各种复杂的原因,红外成像系统的各个组成单元,比如红外辐射场景、大气传输通道、红外光学系统、焦平面阵列、读出电路、应用电子系统、显示系统和工作环境等都存在非均匀性,并具有逐级传递特性。利用非线性动态系统的微分方程组作为各子系统非均匀性的一般抽象模型,可以解决各自系统构成性质的差异,方程组如公式(1)所示:

式中:

$t$ 为时间变量;$u\left( t \right)$ 为输入变量;$x\left( t \right)$ 为状态变量;$y\left( t \right)$ 为输出变量;$\dot x\left( t \right)$ 为状态变量的一阶导函数;$f\left( \cdot \right)$ 和$h\left( \cdot \right)$ 为时域函数。其中状态变量可能包含多个状态参数,即:公式(1)表明系统非均匀性具有时变特性,会造成定标校正方法时间失效等问题。根据广义非均匀性,暂不考虑其时变特性和状态变量的具体变化关系,则可得:

式中:ij为像元空间位置;

$\Delta {u_{ij}}$ 为输入变量的空间波动;$\Delta {x_{ij}}$ 为状态变量的空间波动;$\Delta {y_{ij}}$ 为输出变量的空间波动。工程实践证明:红外成像系统在正常工作参数范围内具备局部线性特征,因此,对公式(3)进行一阶泰勒级数展开并整理可得:公式(4)表明:输出非均匀性与输入变量和状态变量的变量值及其偏导函数值有关。当偏导函数值恒为零时,表明系统无非均匀性,否则非均匀性的响应为非线性函数。非均匀性测量一般是在某个确定的工作点进行的,即

$y$ 、$x$ 、$u$ 及其偏导函数值均为确定的数值。将其代入公式(4)可将各变量归一化为相对变量,消除各种变量的物理量纲及数值范围的巨大差异,便于分析其级联传递特性,简化后公式如下:其中:

公式(5)表明:系统输出非均匀性由输入非均匀性

${\rm{d}}{u_{ij}}$ 和状态非均匀性${\rm{d}}{x_{ij}}$ 及其相对增益组成。当输入变量无非均匀性或可以忽略时,状态变量非均匀性仍会产生输出非均匀性。当状态变量无非均匀性或可以忽略时,输入非均匀性仍然仍会产生输出非均匀性。相对增益系数${h_x}$ 和${h_{\rm{u}}}$ 不恒为1,表明系统非线性会引起输入非均匀性和状态非均匀性的缩放。 -

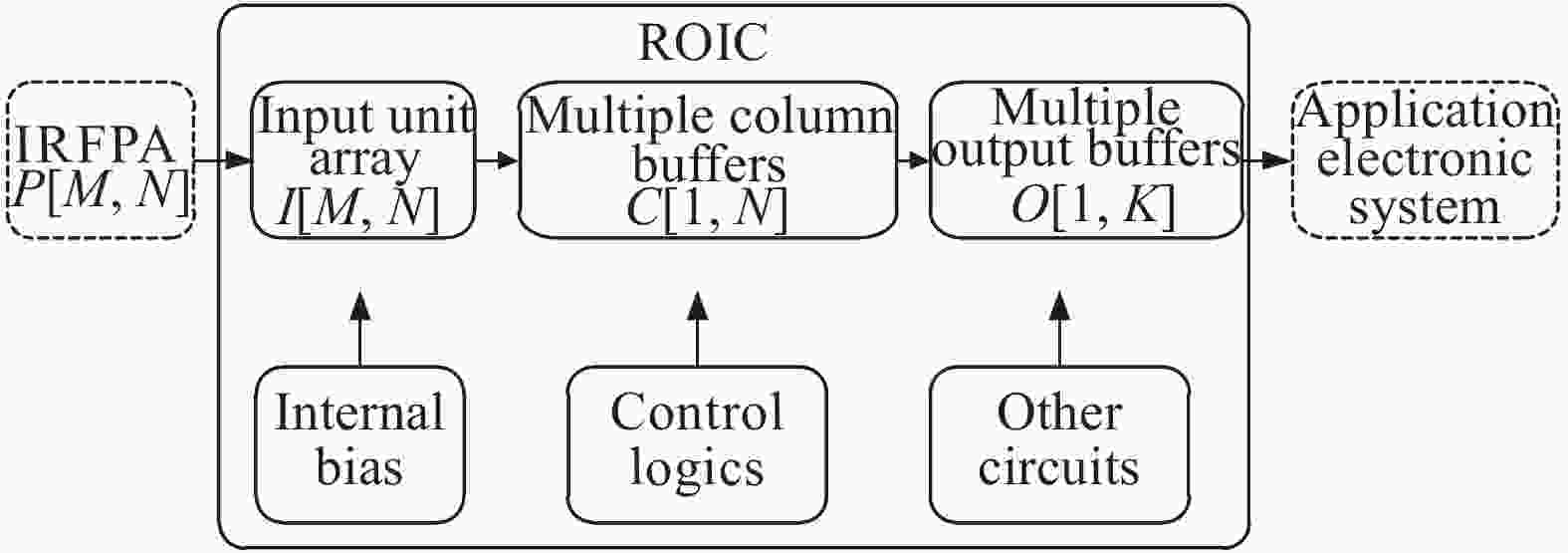

目前,主流IRFPA读出电路均为模拟型行列并串读出结构,与光敏元阵列等尺寸的输入单元阵列对光电流进行积分放大,在逻辑电路的控制下对像素信号逐行逐列进行模拟调理和缓冲输出,最后由输出缓冲电路进行多路串行输出[12],内部偏压、控制逻辑等电路为模拟链路提供辅助,整体如图1所示。

为了减少输出互连,ROIC会多次进行并串转换。一般输入单元阵列与IRFPA阵列保持相同尺寸,多路列缓冲则为单行同列尺寸,多路输出缓冲的最大尺寸则与阵列规模有关,小规模为单路,中等规模为4路,大规模则为8路或以上。这种串并转化会造成阵列数据在传递过程中的排列形式显著变化,导致使用公式(5)进行级联分析存在困难。根据图1的结构可对列缓冲电路和输出缓冲电路的非均匀性矩阵进行等长改造,可得读出电路的总体非均匀性传递矩阵方程如公式(7)所示。

其中:

式中:

$h$ 表示各单元电路的偏导函数值;下标o、c、i分别代表输出缓冲、列缓冲和输入缓冲电路;下标y、x、u分别代表输出、状态和输出变量;M、N、K分别为IRFPA阵列的行、列尺寸及输出通道数;矩阵${D_u}$ 、${D_{{{x}{\rm i}}}}$ 、${D_{{{x}{\rm c}}}}$ 、${D_{{{x}{\rm o}}}}$ 分别代表光伏像素阵列、输入单元阵列、列缓冲电路、输出缓冲电路的非均匀性的信号波动量传输矩阵;行向量${V_{{{x}{\rm c}}}}$ 是列缓冲电路的状态非均匀性向量;行向量${V_{{{x}{\rm o}}}}$ 是输出电路的状态非均匀性向量;函数$repmat\left( \cdot \right)$ 用于把向量按指定的行列数重复获得等尺寸的非均匀性传输矩阵。 -

分别对噪声模型、多通道传输、非线性、某320×256读出电路进行Matlab建模仿真,并利用仿真图像和空间噪声进行定性和定量评估。其中,空间噪声可采用三维噪声模型[5]中的4个空间噪声项:帧空间噪声

${\sigma _{\rm{s}}}$ 为整帧数据的均方根,与非均匀性指标数值相同;行空间噪声${\sigma _{\rm{v}}}$ 为帧内每行数据均值的均方根;列空间噪声${\sigma _{\rm{h}}}$ 为帧内每列数据均值的均方根;像元空间噪声${\sigma _{{\rm{vh}}}}$ 为帧空间噪声去除行、列空间噪声后的余量。式中:

${d_{ij}}$ 为第i行j列数据;$\overline D $ 为整帧数据的均值;${v_i}$ 为第i行数据的均值;${h_j}$ 为第j列数据的均值。 -

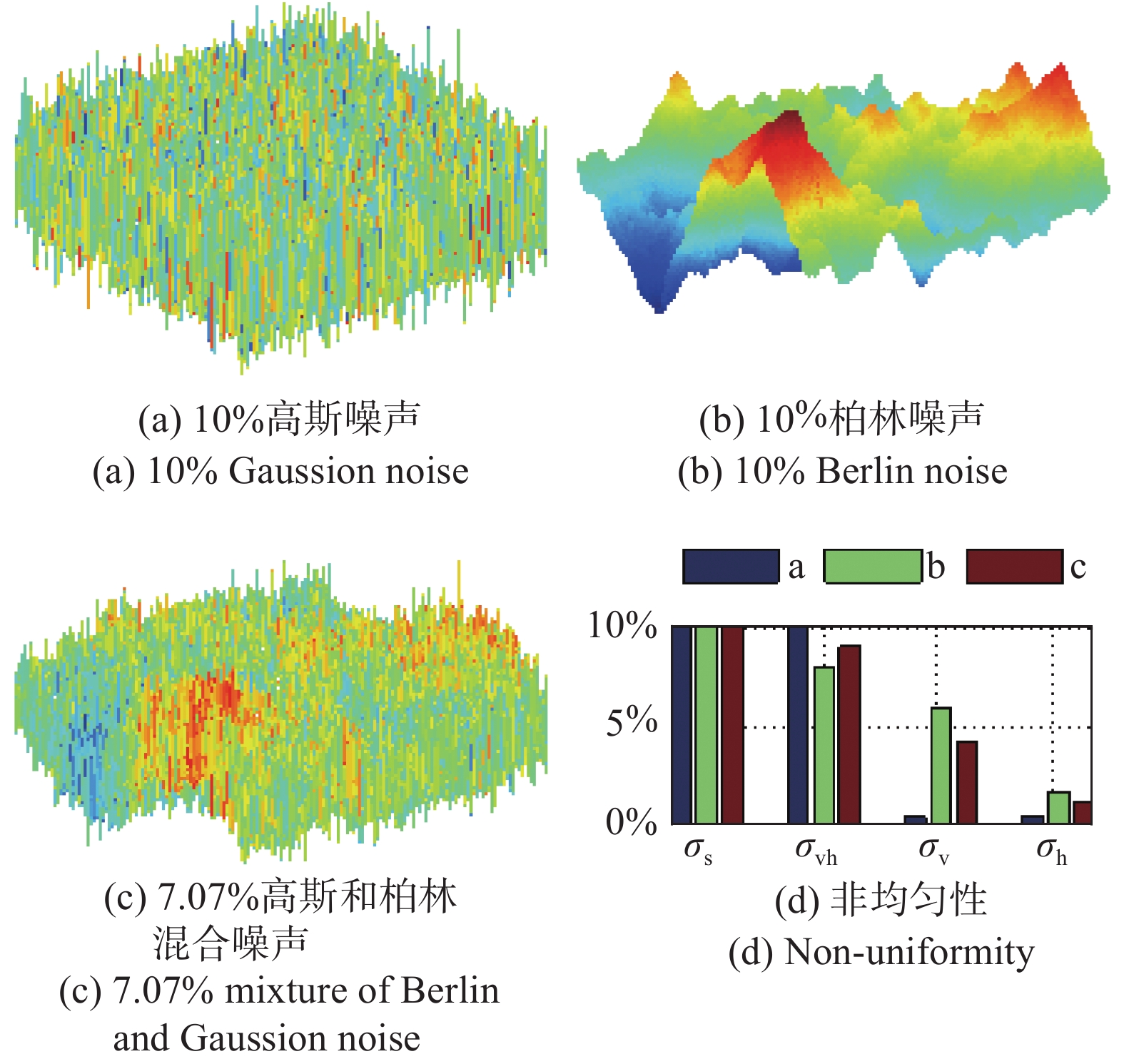

读出电路参数的空间波动可以看作是一种随机噪声,并利用特定统计特征的噪声模型进行模拟。由于读出电路参数的波动特征具有一定的局部空间相关性,比较适合采用柏林噪声进行模拟,但是由于插值效应,柏林噪声局部数值较为平滑,无法体现分时采样过程中时域噪声对空间噪声的影响。高斯噪声模型基本不存在局部相关性,但是可以模拟出分时采样的时空噪声转换特性。因此,文中采用柏林噪声叠加高斯噪声来模拟读出电路的空间波动,仿真结果如图2所示。图中,柏林噪声具有明显的行间非均匀性和列间非均匀性,而高斯噪声则主要体现为像元非均匀性。

-

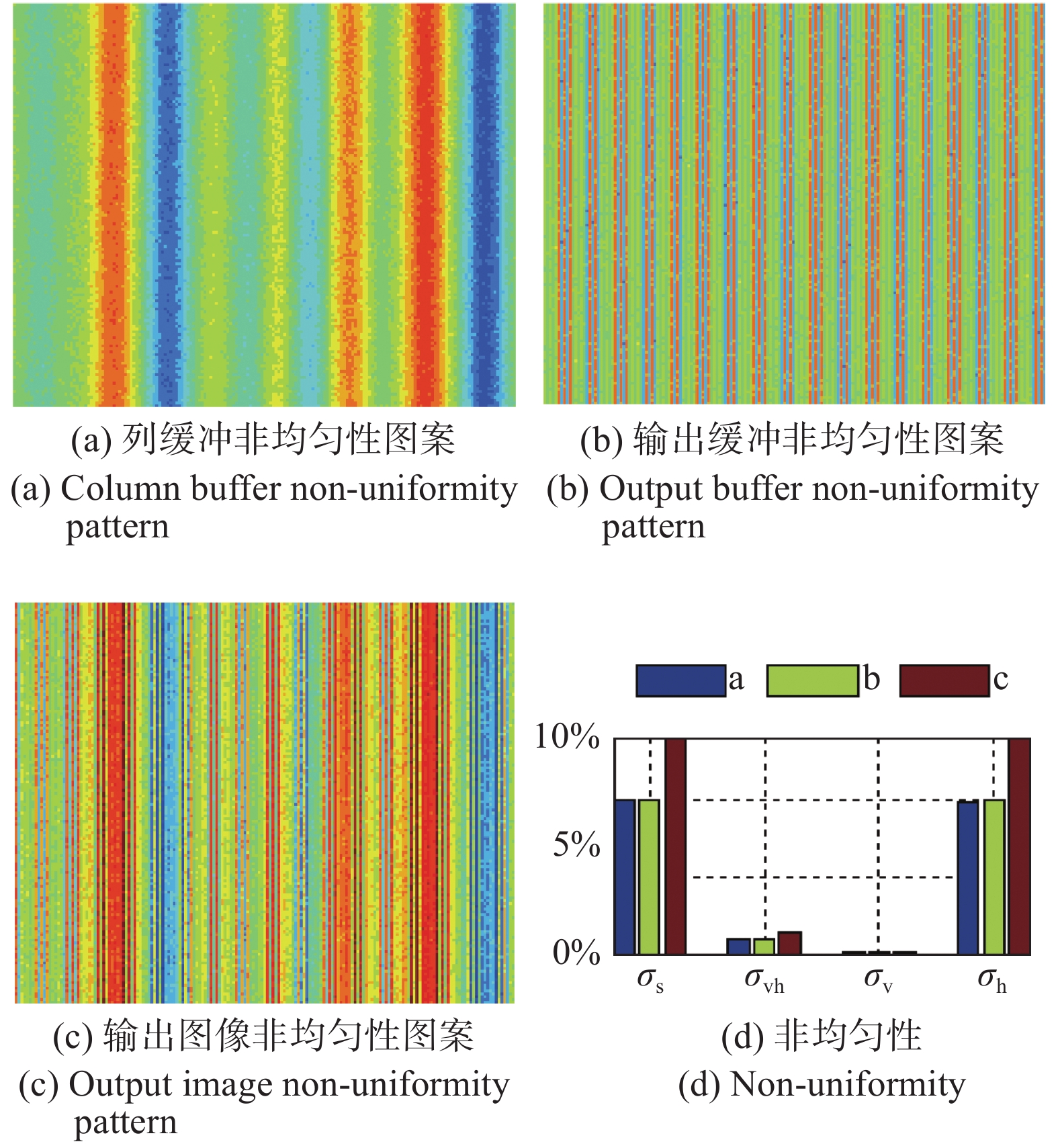

像素信号在读出电路中需要通过多通道的列缓冲和输出缓冲电路进行并串转换传输,通道间的状态参数差异会引入显著的非均匀性。假定输入信号和输入电路是均匀的且系统是完全线性的,即输入非均匀性为零且相对增益均为1,只有列缓冲电路和输出缓冲电路存在状态非均匀性,则仿真结果如图3所示。

图3表明多通道列缓冲和多通道输出缓冲电路理论上只会引入列间非均匀性,但是分时采样过程中的时间噪声(采用1%高斯噪声模拟)会转变为空间噪声,主要表现为少量的像元非均匀性,量级由对应参数时域噪声强度及其噪声抑制系数决定。

-

一般而言,读出电路的非线性定义为在所关心的电压范围内,实际曲线和理想曲线的最大偏差与最大输出摆幅的比值[2]。根据非线性误差的定义,结合公式(5)和公式(7)采用折线模型进行局部线性化简可得:

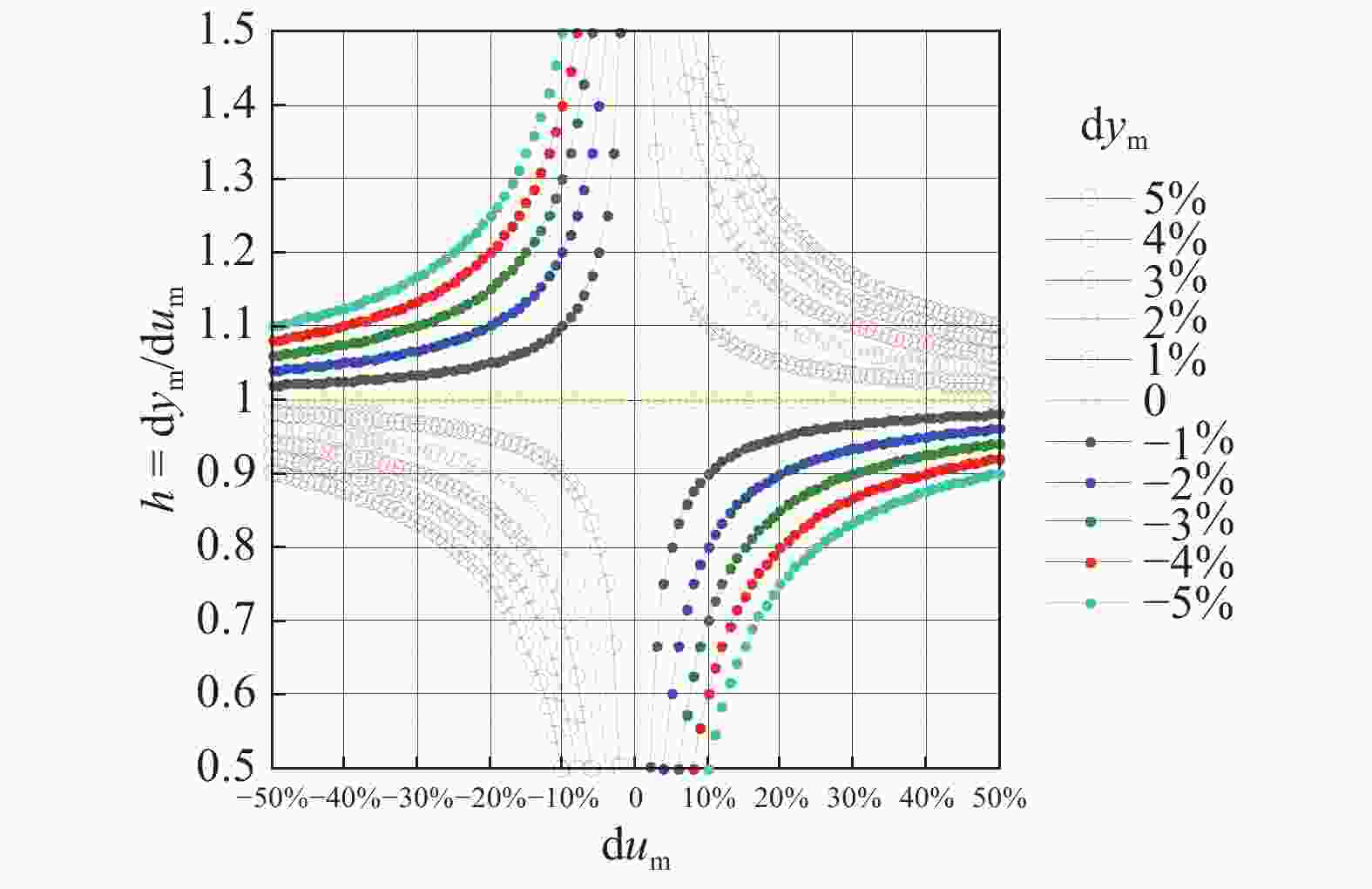

式中:H为系统输入线性响应的系数,令H =

${{{y_{\max }}} / {{u_{\max }}}}$ 进行归一化可得前述非线性误差${\rm{d}}{y_{\rm{m}} }$ ,而${\rm{d}}{u_{\rm{m}} }$ 则为${\rm{d}}{y_{\rm{m}} }$ 对应的输入信号相对变化量。利用公式(10)可得不同非线性条件的非均匀性增益曲线,如图4所示。当不存在非线性(

${\rm{d}}{y_{\rm{m}} } = 0$ )时,读出电路对输入信号的非均匀性无缩放($h = 1$ ),否则非线性会造成输入信号的非均匀性发生缩放,缩放比例与非线性的幅度及其变化率成正比。一般读出电路的非线性幅度都能控制在1%以下[13],但是常规定义的非线性无法表征局部的非线性变化情况,当局部非线性变化率较大时,也会造成明显的非均匀性缩放。因此,评估非线性非均匀性时宜采用文中提出的考虑了局部变化率的相对非线性。 -

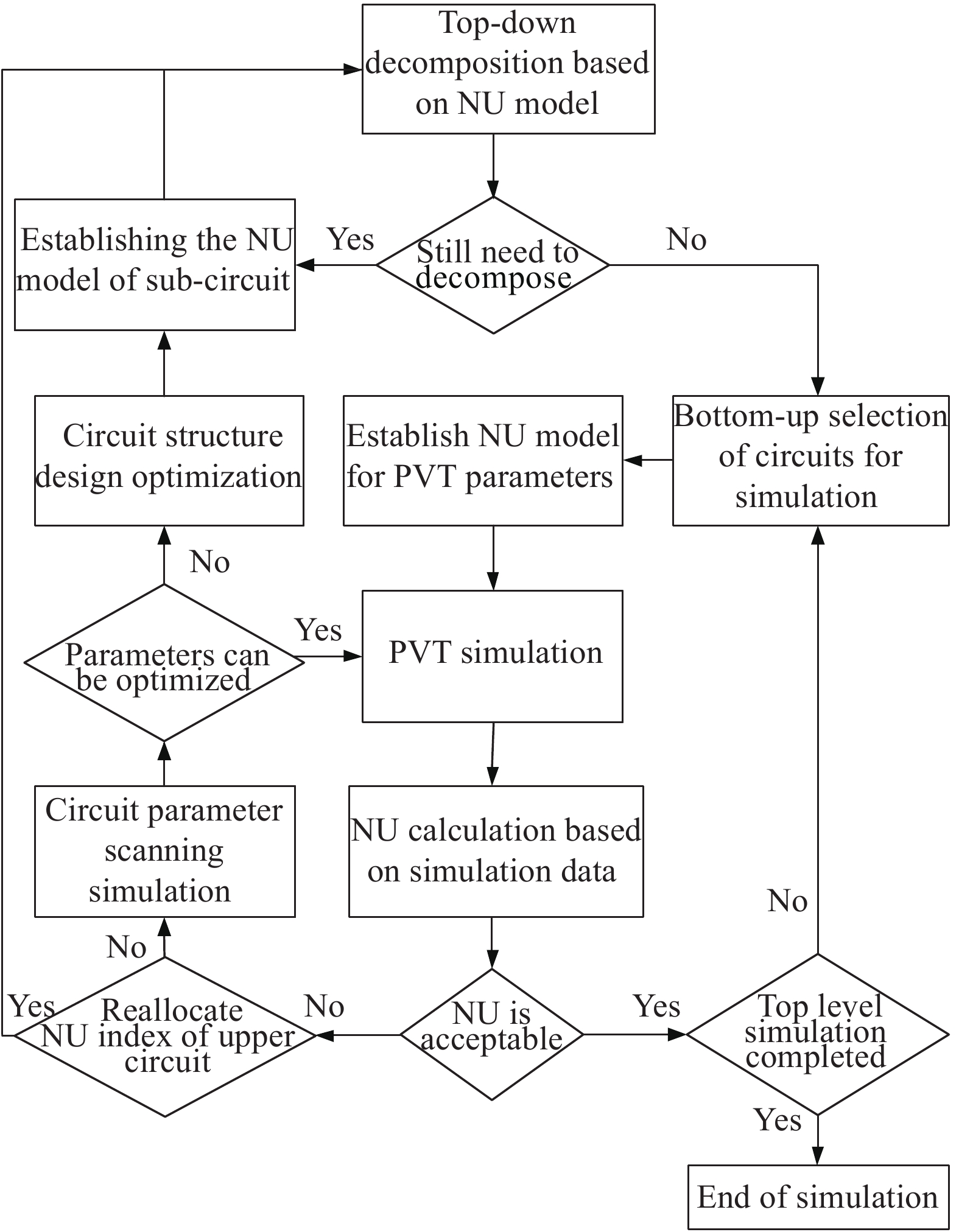

利用模型指导某320×256电路非均匀性指标的仿真优化基本流程如图5所示。

-

该电路的总体非均匀性传递模型如公式(7)所示,其中

$M = 256,\;N = 320,\;K = 4$ 。假定公式(7)中的非均匀数据矩阵${D_u}$ 、${D_{{{x}{\rm i}}}}$ 、${D_{{{x}{\rm c}}}}$ 、${D_{{{x}{\rm o}}}}$ 是相互独立的随机变量,结合公式(9)可得:该电路非均匀性指标(帧空间噪声)的分解公式如下:该电路输出的非均匀性指标,即

${\sigma _{{\rm{sy}}}}$ 的设计要求为不大于10%。整体上先将非均匀性分为与输入有关和与电路状态有关的两大部分,暂时假定二者影响相同,代入公式(11)可得:根据2.3节分析,暂时假定公式(12)中各系数的局部相对非线性指标的初始边界为10%,则代入上式可得各子单元非均匀性指标的初始设计要求如下:

该电路第一层分解的输入单元、列缓冲、输出缓冲等子电路都是阵列结构,其功能单元电路的规模都不大,可不再分解。

-

当前读出电路主要采用CMOS工艺实现,这种工艺存在较大片内器件差异(intra-die device variations),即同一器件在同一芯片不同区域的参数差异较大。由于器件参数众多,代工厂一般采用能够覆盖三西格玛偏差范围的五点工艺角模型来表征工艺线的参数偏差。此外,温度和电压也对器件参数有重要影响。因此,可采用PVT(Process,Voltage,Temperature)组合条件对电路的空间噪声进行评估。

假定PVT参数的空间噪声是相互独立的,则子单元电路输出空间噪声是四者空间噪声响应的叠加。为了消除不同状态参数增益

${h_{\rm{x}}}$ 的单位及数值差异,可将其与状态变量的乘积直接等效至输出变量${\rm{d}}{y_{ij}}$ 。另外,状态参数空间噪声幅值很小,其增益系数的非线性暂不考虑。则根据公式(5)和(7)建立单元电路的PVT非均匀性模型如公式(14)所示。式中:

${D_y}$ 代表输出空间噪声;${D_{\rm{P}}}$ 、${D_{\rm{V}}}$ 、${D_{\rm{T}}}$ 分别代表PVT参数的等效输出噪声。据此即可利用初始设计的边界条件对子单元电路进行PVT仿真并获得其非均匀性。首先,对外部设计约束T参数进行仿真。以该电路T参数的初始条件80±0.1 K对输入输出响应曲线进行温度偏差扫描,计算仿真数据的方差作为随机变量

${D_{\rm{T}}}$ 的统计方差。各子电路的仿真结果均表明:0.1 K温度波动造成的空间噪声可忽略不计。其次,V参数既有外部约束也有内部约束,为了提高电路偏压适应性,其初始条件的边界暂定为±5%。V参数数量较多,如列缓冲单元电路有6个偏压输入,可逐一对输入输出响应进行电压偏差扫描,计算全部V参数仿真数据的方差之和作为随机变量

${D_{\rm{V}}}$ 的统计特征。第三,采用五点工艺角模型进对输入输出响应进行工艺偏差扫描,计算仿真数据的方差作为随机变量

${D_{\rm{P}}}$ 的统计方差。第四,对当前设计的输入输出非线性进行仿真,根据仿真数据和公式(10)计算

${\rm{d}}{y_{\rm{m}} }$ 及其对应的${\rm{d}}{u_{\rm{m}} }$ 。最后根据公式(14)和公式(9)计算出子单元电路的非均匀性,然后与分解的指标对比,确定是否满足设计要求,如不满足则需优化设计。

该电路各子单元初始设计的仿真结果如表1所示。三个子单元的非均匀性均不满足初始设计分配要求,需要优化设计。局部相对非线性虽然比常规非线性指标要高很多,但最高的输入单元也只有约5.1%的相对非线性,可以满足10%的初始设计要求。

Parameters name Symbol Values Array size N×M 320×256 Process corners P [FF,SS,TT,FS,SF] Voltage tolerance of biases dV ≤5% Temperature variation dT ≤0.1 K Du variation dDu 5% Dxi variation dDxi [6.7%,0.3%] Vxc variation dVxc [11.7%,5.5%] Vxo variation dVxo [18.3%,0.9%] Relative nonlinearity of hui dymi/dumi 1.1%/21.4% Relative nonlinearity of huc dymc/dumc 0.7%/22.5% Relative nonlinearity of huo dymo/dumo 0.03%/2.1% Table 1. PVT simulation of 320×256 ROIC

电路优化主要包括参数优化、结构优化和总体优化三部分。如果当前仿真结果已经接近设计要求,首先考虑其他子电路是否对状态噪声不敏感,可以压缩其设计指标,重新对设计指标的分配进行总体优化。参数优化主要针对P、V参数,按敏感度对V参数进行扫描,确定其合理可接受的边界下限,然后对电路元件参数进行扫描优化,寻找工艺角对电路输出影响较小的区域。如仍无法满足要求,则需要从电路结构上进行优化设计。以上优化过程需要进行多次综合迭代。

该电路经过参数优化后,输入单元和输出缓冲单元的状态非均匀性分别从6.7%和18.3%下降到了1%以下,可满足初始分配要求。虽然列缓冲单元的状态非均匀性5.5%仍不满足初始分配要求,但是把仿真数据代入公式(11)计算该电路输出的总体非均匀性指标,约为7.8%,可以满足10%的总体指标要求。因此,按照当前结果重新分配设计指标,综合考虑可以暂时结束设计优化过程。

如果该电路后续改进型的非均匀性指标要求提高到7.8%以下,则需进一步优化设计,特别是需对列缓冲单元电路进行结构优化。

-

仿真结果表明:读出电路具有明显的非均匀特性,但通过设计优化可以有效降低。某320×256电路经优化后,输入单元和输出缓冲单元的状态非均匀性分别从6.7%和18.3%下降到了1%以下,但是列缓冲电路的仍有5.5%的非均匀性。因为该电路的列缓冲单元在结构上采用了比较多的压控电流镜模块,仅靠参数优化无法进一步降低非均匀性,必须进行结构优化。

根据表1数据可以计算读出电路自身的非均匀性为5.7%,其中非线性非均匀性约0.5%,状态非均匀性约5.6%,因此,状态非均匀性占主要地位。状态非均匀性主要来自于器件工艺参数的空间波动和关键偏压参数的空间随机波动;由于工作在低温制冷条件下,读出电路的温度参数空间波动较小,对非均匀性的影响基本可忽略。该电路的相对非线性的数值虽然高于常规非线性,但仍属于乘性噪声,对非均匀性的影响基本可忽略。

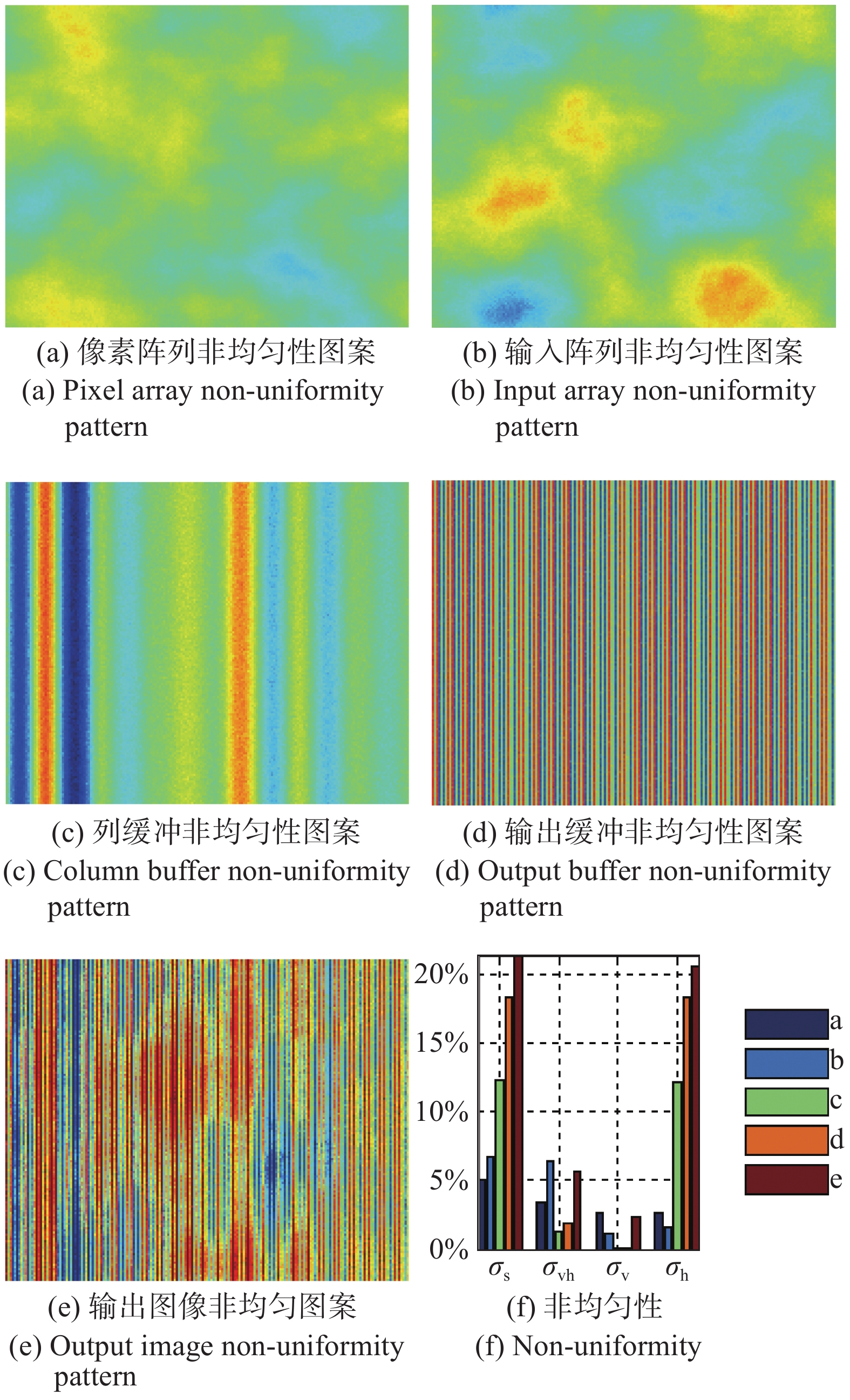

对电路优化前后的仿真数据进行主观图像模拟和三维噪声评估,分别如图6和图7所示。图中,像素阵列是指光伏二极管阵列;输入阵列是指ROIC的输入单元电路阵列;列缓冲是指ROIC的多通道列缓冲电路;输出缓冲是指ROIC的多通道输出缓冲电路;输出图像是指ROIC的最终输出。图6显示读出电路的非均匀性超过了输入的非均匀性,造成输出非均性显著增大,输出图像上叠加了严重的条纹噪声,输出图像的空间噪声受读出电路空间噪声支配。图7表明:电路优化后,电路的非均匀性以列缓冲电路空间噪声为主,如要进一步降低输出图像的非均匀性,应以列缓冲电路优化设计为主。

基于该模型的非均匀性仿真结果是读出电路输出空间噪声的随机抽样数据的标准差,本身也是一个随机变量。与单只器件测试数据的对比意义不大,只有大量器件测试数据的统计值才能用于模型参数的推导和修正。另外,由于光伏阵列和子单元电路的空间噪声分布特征不同,可以利用三维噪声的统计值评估非均匀性的主要来源。例如,列缓冲电路主要表现为低频的列空间噪声,输出缓冲电路则主要表现为高频列空间噪声,光伏阵列和输入单元则主要表现为像元空间噪声和行空间噪声。

受测试手段限制,暂时无法对读出电路芯片直接进行测试验证。测试验证主要包括芯片测试方法、测试数据统计模型和测试数据到模型反向传递3个方面。其中,芯片测试方法主要考虑读出电路的可测试性设计,包括激励注入电路及片上测试电路的设计;数据统计处理主要考虑小样本量及不同数据的统计模型问题。模型数据反向传递主要是结合非均匀模型和测试方法综合考虑,确定可传递参数和需测试参数。

图8是320×256电路仿真结果与17只探测器组件非均匀性测试数据的三维噪声对比图。图中黑色粗虚线为仿真结果,红色线为最差测试数据,蓝色线为最好测试数据。对比可知,大部分测试数据的三维噪声分量都在仿真结果的边界内,少量数据超出了仿真结果的边界。对于抽样分布的统计特征来说,当抽样样本量增大时,抽样测试数据的均值会接近文中的仿真结果。由于测试样本使用的是经过筛选的读出电路且数量较少等原因,导致抽样分布趋向于正偏态分布的形式,使得其众数优于均值。为验证模型准确性,未来必须对读出电路的可测试性进行优化,以便对读出电路直接测试,并对测试数据进行累积和统计。

除上述测试验证问题外,未来还需在低温模型、噪声及PVT参数统计特征、电路优化理论等方面开展进一步研究和测试。

-

根据红外焦平面成像系统非均匀性的特点,提出了一种采用局部线性化原理建立读出电路非均匀性传输模型的方法,从理论上证明:其非均匀性由非线性缩放和PVT参数波动两部分构成,其中非线性缩放部分一般可忽略。根据该模型对某320×256读出电路进行仿真验证,结合电路仿真获取了非均匀性模型的统计参数,并利用图像和三维空间噪声进行定性和定量评估,结果表明:读出电路的非均匀性对探测器的非均匀性指标有直接影响。

该方法可以作为读出电路非均匀性的总体设计评估工具,并结合电路仿真进行非均匀性指标分配与优化,支撑自顶向下的读出电路非均匀性设计过程。

Study on non-uniformity of ROIC for IRFPA

doi: 10.3788/IRLA20190581

- Received Date: 2019-12-25

- Rev Recd Date: 2020-01-16

- Available Online: 2020-05-26

- Publish Date: 2020-08-28

-

Key words:

- ROIC /

- IRFPA /

- non-uniformity /

- simulation

Abstract: The ROIC has an important influence on the non-uniformity of the IRFPA device. The non-uniformity model of general system unit was established by using the Taylor series of the dynamic nonlinear system function, and the ROIC non-uniformity model was established according to common architecture of analog ROIC. The spatial distribution characteristic of circuit statur parameters was modeled by mixing Berlin noise and Gaussion noise. The non-uniformity was evaluated with the spatial components of standard three demensions noise model. The time to sptial convertion from array signals to serial outputs was simplified by equal size convertion matrix. The non-uniformity of noise, multi-channel buffers and resposing nonlinearity were analized. The non-uniformity of a 320×256 array ROIC was evaluated by simulation and improved by circuit optimization based on the proposed model. Simulaiton results show that it can be used to evaluate the non-uniformity and to assist with non-uniformity engineering optimization of ROIC at the system level.

DownLoad:

DownLoad: